FCom FCO系列差分输出晶体振荡器涵盖2.5×2.0至7.0×5.0多种封装,提供LVPECL、LVDS与HCSL三种标准接口,频率支持13.5MHz至220MHz,并具有出色的相位抖动指标(典型值0.15~0.3 ps RMS)。本指南将基于应用场景总结输出类型、电气匹配建议及典型芯片平台,辅助系统设计工程师快速完成时钟器件选型。

一、差分输出格式选择建议

- LVPECL:推荐用于高速SerDes与光模块,驱动能力强,需终端电阻至VDD-2V。

- LVDS:低功耗、低EMI,适合ADC/DAC、PHY、同步SoC等差分输入器件,建议100Ω差分端接。

- HCSL:专为PCIe总线接口设计,使用50Ω至GND端接,适用于主板类系统。

二、电源布局与信号布线建议

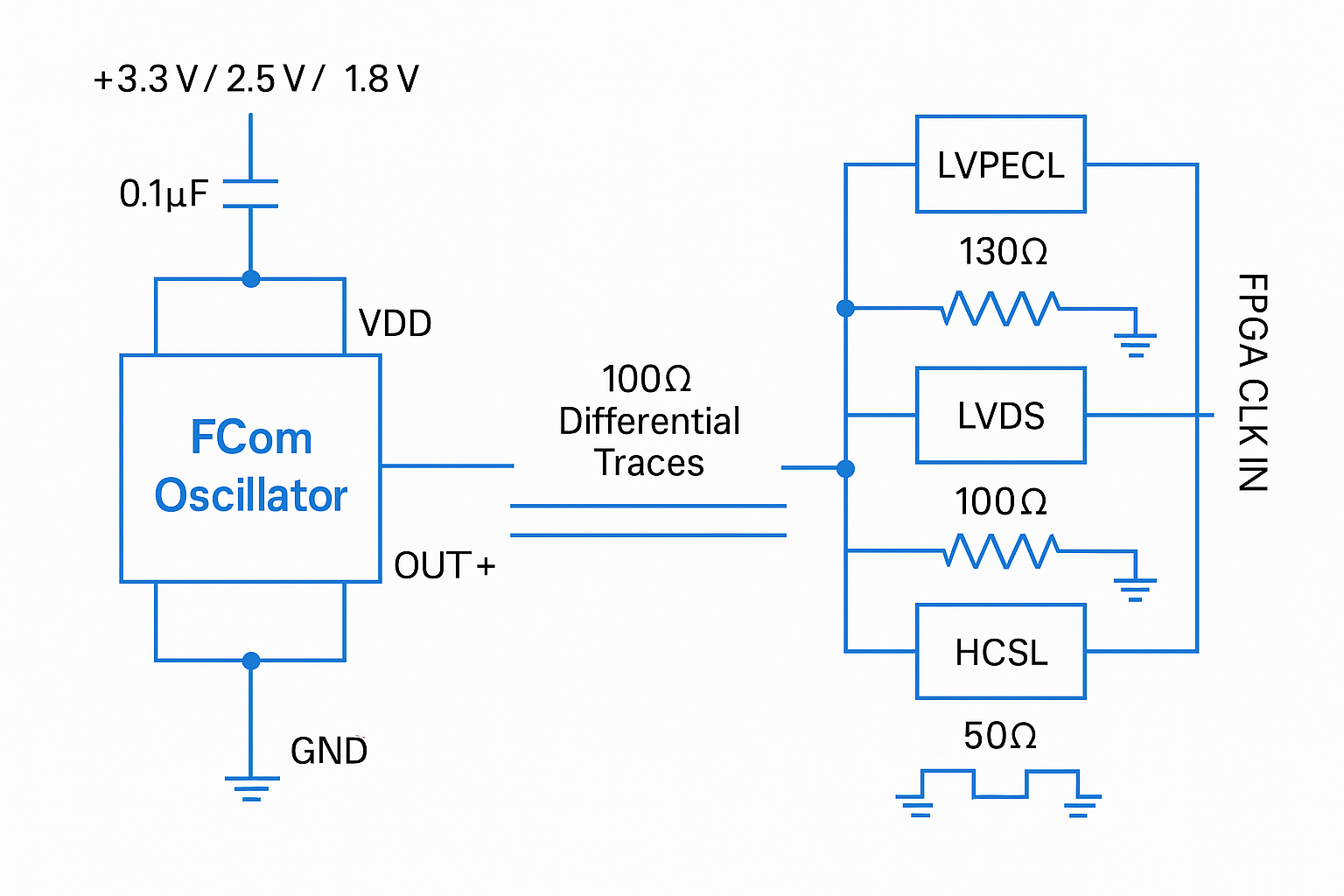

- 在VDD与GND之间紧贴晶振器件放置0.1μF去耦电容,可显著抑制电源噪声传导。

- 差分输出建议使用等长等阻抗布线(100Ω),避免跨层不连续与异层参考地问题。

- HCSL信号需每路接入50Ω至GND的终端电阻。

三、参考原理图结构

原理图布局结构

原理图布局结构

四、封装与系统平台部署建议

- FCO-2L:适合SFP光模块、无线模组、尺寸敏感设计

- FCO-3L:主流嵌入式平台与同步接口控制模块

- FCO-5L:网络设备、交换机主板、工业控制系统

- FCO-7L:高频服务器主板、基站控制板、大功耗场景

五、差分晶体振荡器典型芯片匹配方案

在差分晶体振荡器的系统设计中,确保时钟信号与接收芯片的电气特性完美匹配,是保证整体时序稳定与抖动抑制的关键。FCom在长期产品应用过程中,归纳出覆盖SerDes、高速ADC/DAC、以太网PHY、时钟清理器、SoC平台、光通信控制器及PCIe等多个核心应用的推荐芯片搭配表。

应用类型 |

芯片型号 |

芯片特点与说明 |

FCom推荐型号 |

推荐频率 |

推荐输出模式 |

| SerDes芯片 | Analog Devices ADN2817 | SONET/SDH CDR,需LVPECL时钟输入 | FCO-2L | 155.52 MHz | LVPECL |

| SerDes芯片 | Semtech GN2104 | 10G/25G SerDes,常用于SFP+/QSFP模块 | FCO-2L | 156.25 MHz | LVPECL |

| SerDes芯片 | MACOM M37046 | 28G/56G SerDes,应用于高速有源线缆 | FCO-2L | 161.1328 MHz | LVPECL |

| SerDes芯片 | TI DS100BR410 | 3.125~10.3Gbps差分驱动器 | FCO-3L | 100 MHz | LVDS |

| 光模块控制器 | Semtech GN2104 | 集成CDR,适用于10G光模块 | FCO-2L | 155.52 MHz | LVPECL |

| 高速ADC/DAC | ADI AD9208 | 14-bit, 3GSPS JESD204B接口 | FCO-5L | 122.88 MHz | LVDS |

| 高速ADC/DAC | TI DAC38RF82 | JESD204B高速DAC | FCO-5L | 122.88 MHz | LVDS |

| PHY芯片 | Marvell 88X3310 | 多速率以太网PHY | FCO-3L | 156.25 MHz | LVDS |

| SoC芯片 | NXP LX2160A | 16核网络处理器 | FCO-5L | 100 MHz | LVDS |

| 时钟芯片 | TI LMK04828 | 低抖动时钟清理分配器 | FCO-3L | 100 MHz | LVDS |

| PCIe控制器 | Renesas 9DB206 | x16 PCIe缓冲芯片 | FCO-7L | 100 MHz | HCSL |

六、常见问题与解决方案

问题 |

可能原因 |

建议措施 |

| 输出抖动大 | 电源噪声或布局不良 | 靠近VDD放置去耦电容,走线对称 |

| 频率漂移明显 | 未终端或负载影响 | 确认终端阻抗,选用±25ppm或更严精度型号 |

| 启动无输出 | OE引脚控制逻辑错误 | 拉高或悬空OE测试基本功能 |

| 信号摆幅不符 | 接口类型配置不匹配 | 核对输出模式与接收芯片规范 |

| 温度变化频偏 | 选型温宽不足 | 选用-40~125℃宽温版本 |

- 随机文章

- 热门文章

- 热评文章

- 泰克MSO5系列示波器如何提升电源噪声测试精度

- 如何破解三菱PLC与西门子PLC的通讯难题

- 从江苏绿茵场到工业4.0赛场:全志HZ-T536_EVM如何‘踢’出智能制造新局?

- 凯米斯科技COD-408在线COD传感器:开启水质监测新时代

- 洁净室用特殊光谱(黄光)论述-江苏泊苏系统集成有限公司

- 端侧/边缘AI盛宴正在成局——GPU成为关键推手

- 新股前瞻|银屑病赛道新药扎堆,和美药业何以红海“突围”?

- 华纳药厂:国盛证券有限责任公司、东吴证券股份有限公司等多家机构于6月11日调研我司