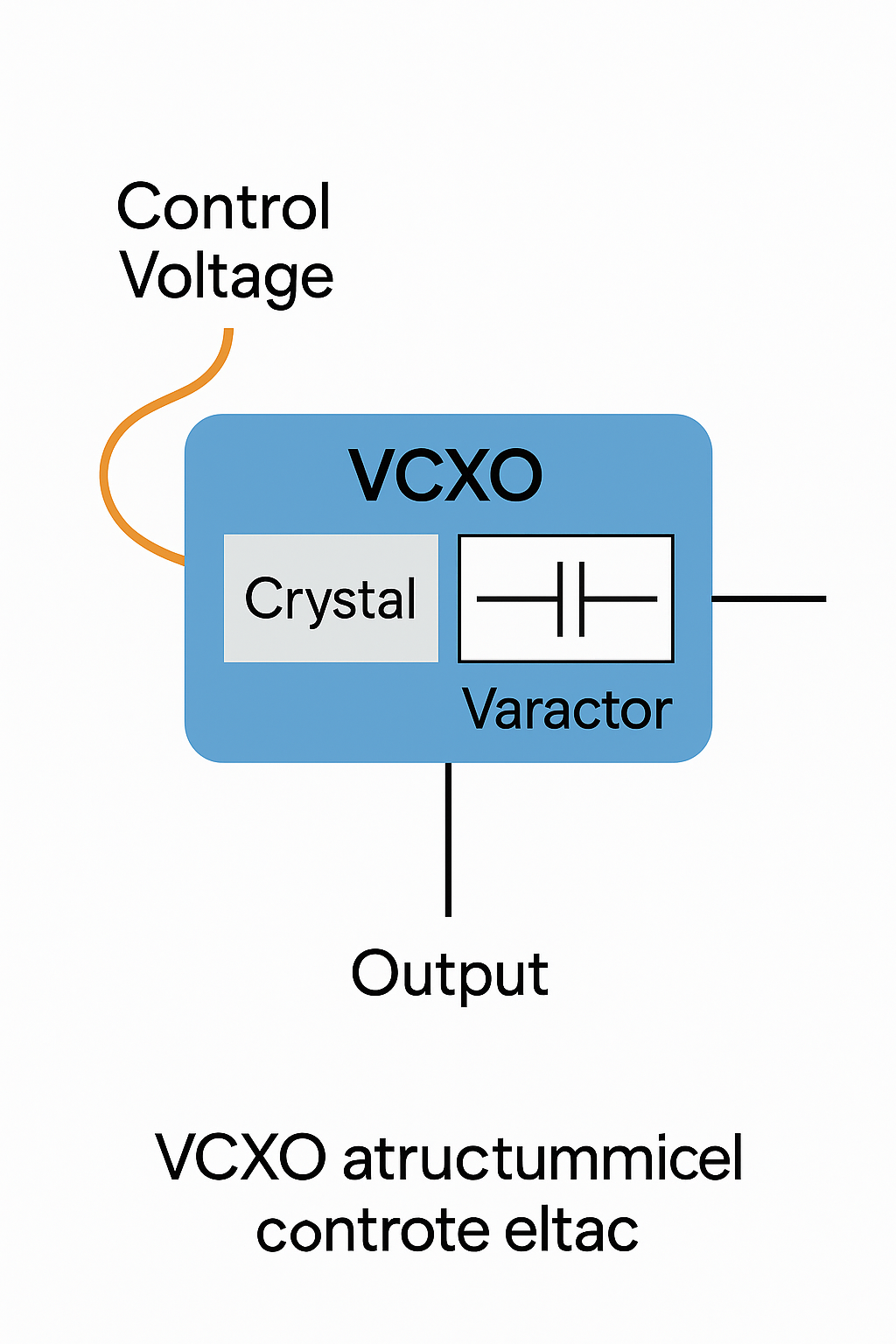

在高速数字系统和复杂时钟架构日益发展的背景下,传统固定频率晶体振荡器难以满足灵活调频、低抖动和短交期的工程需求。具备±50ppm~±150ppm拉力范围与1~3天快速交付能力的可编程VCXO振荡器,凭借其在可调性、低相位噪声和交付效率方面的显著优势,已成为FPGA、ADC、通信模组及网络设备领域的新一代时钟核心。

什么是可编程VCXO?

可编程VCXO(Voltage Controlled Crystal Oscillator)是一类结合可编程频率设定与电压控制调频机制的晶体振荡器。它允许工程师通过I²C、EEPROM或工厂预设方式快速定义目标频率,并通过外加控制电压实现±50~±150ppm范围内的精细频率调整。这种能力极大地提升了系统对同步精度的控制能力,特别适合动态频率配准、锁相环(PLL)时钟生成和ADC/DAC采样速率控制等高精度应用。

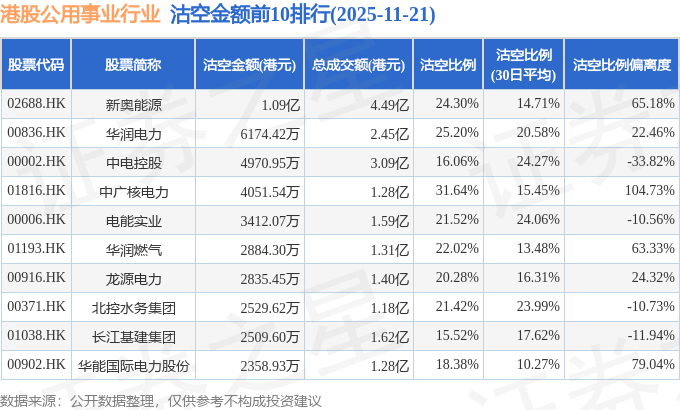

VCXO结构原理图:包含晶体、变容二极管与控制电压调谐机制

VCXO结构原理图:包含晶体、变容二极管与控制电压调谐机制

低抖动输出的重要性

在高速数据通路中,信号的相位稳定性对误码率和数据恢复精度有决定性影响。可编程VCXO通常具备0.6ps RMS以内的相位抖动性能,可显著优化系统边沿检测与锁定时序。在PCIe、SONET、10G以太网和高速采样转换场景中,低抖动VCXO可显著降低眼图收缩、提高串行通信的抗干扰能力,并确保ADC/DAC模块在高速模式下保持采样精度。

±50~±150ppm拉频范围的工程优势

拉力范围决定了VCXO在PLL环路或时钟调整过程中可容忍的电压调节深度。±50ppm适用于常规频偏校准;±100ppm~±150ppm则更适合用于跨设备同步、频率漂移补偿与RF系统调谐。具备广拉频能力的VCXO可以有效配合DPLL芯片、时钟冗余系统或基准频率偏移调节机制,从而在不更换晶体源的前提下,兼容更广泛的系统平台与通信协议。

典型应用与推荐配置

1. FPGA平台锁相输出:推荐频率:100MHz、125MHz,控制器件:Xilinx Zynq Ultrascale+,建议使用±100ppm拉力,LVDS输出;

2. 高速ADC/DAC时钟同步:频率范围:80MHz~160MHz,适配芯片:TI ADC12DJ3200、ADI AD9689,推荐±150ppm拉力,抖动要求≤0.6ps RMS;

3. 网络交换与路由平台:频率点:156.25MHz、312.5MHz,用于PHY或MAC接口同步,推荐LVPECL输出;

4. 可重构无线模块:频率:20~80MHz,适配SoC/MCU:NXP i.MX RT1170、Espressif ESP32-S3,拉力范围±50~100ppm。

可编程VCXO应用实例图:含FPGA、ADC、通信芯片频率匹配1~3天快速交付如何实现?

可编程VCXO的结构允许使用统一硬件,通过快速烧录频率配置完成定制化出货。制造商通过模块化标准化设计和库存管理机制,在收到需求后可在1~3个工作日内完成频点配置与测试。这大幅缩短了传统晶振6~8周交期的限制,尤其适用于打样验证、设计更迭、项目突发调频、或供应链替代需求。

总结

集±50~±150ppm拉力控制、0.6ps低抖动性能与快速交付能力于一身的可编程VCXO振荡器,正引领时钟源向着灵活化、低延迟、高可靠方向发展。其在复杂同步网络、数据采集系统与多协议通信模块中的稳定输出,为高性能电子系统提供了高效、精准的时序支持,是现代数字系统中不可或缺的关键元件。

- 随机文章

- 热门文章

- 热评文章

- “电费拖欠终结者:安科瑞预付费系统如何根治物流园收费顽疾?”

- CoolSiC™ MOSFET Gen2性能综述

- 启源芯动力罗源湾补能中心项目实证:钢-港短倒场景降碳可复制新路径

- 碳化硅MOSFET全桥模块在出口型高端逆变焊机中的应用技术优势

- FUG MCP 1400-1250通讯协议故障排除与硬件修复案例

- PROFINET转DeviceNet网关:西门子S7-1500与ABB机器人高效通信方案

- 永川排水管网“大升级”,8个月焕新城市“地下血管”

- 兴达易控ModbusRTU转ProfibusDP网关在RAC300控制器里的巧妙应用